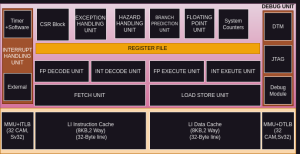

This work focusses on the design and development of a synthesisable 32-bit RISC-V processor core, adhering to the RISC-V Unprivileged ISA specification (RV32I/M/A/F) as well as the machine mode privilege specification. The processor is developed with a clean and modular architecture suitable for ASIC integration and optimised for use in embedded systems and real-time applications, where low-latency response and deterministic execution are critical. What sets this core apart from other RISC-V implementations is the inclusion of physical memory protection (PMP) support, allowing secure access control to different memory regions – a key requirement for embedded and safety-critical systems. In addition, a fully functional debug module has been implemented, compliant with the RISC-V Debug specification. This includes support for single-step execution and register/memory access during halt, and a JTAG interface for external debugger connectivity such as GDB. With its balance of standards compliance, functional completeness, and low-overhead integration, this 32-bit RISC-V processor core serves as a robust and flexible foundation for a wide range of research and industrial applications in embedded system design.

Publications

1. A. Birari, P. Birla, K. Varghese and A. Bharadwaj, “A RISC-V ISA Compatible Processor IP,”

2020 24th International Symposium on VLSI Design and Test (VDAT), Bhubaneswar,

India, 2020, pp. 1-6, DOI: 10.1109/VDAT50263.2020.9190558.

https://ieeexplore.ieee.org/document/9190558