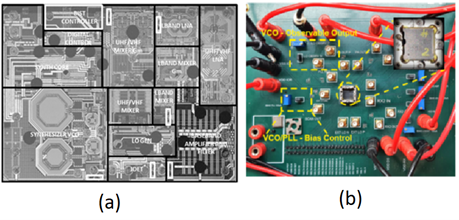

The semiconductor industry, with $600B+ in annual sales, is crucial to the $1T+/year electronics industry. Test costs for mass-produced chips have become comparable to fabrication costs, driving the integration of Built-in-self-test (BIST) features into analog/RF products [1], [2]. Our group at IISc is investigating AI/ML-based techniques to test Analog/RF ICs using DC measurements, which have a significant correlation with RF parameters of interest. By using test data and AI/ML, BIST with DC tests can be used to make Analog/RF testing more efficient [2], saving test time and cost. Collaboration with major semiconductor companies is underway to explore this further.

[1] G. Banerjee, M. Behera, M.A. Zeidan, R. Chen and K. Barnett, “Analog/RF Built-in-Self-Test Subsystem for a Mobile Broadcast Video Receiver in 65-nm CMOS”, IEEE J. Solid State Circuits, vol. 46, no. 9, pp. 1998-2008, Sep. 2011.

[2] G. Banerjee, M. Behera, K. Barnett, Methods and apparatus for providing a built-in self-test, U.S. Patent No. US 8589750 B2, Granted 2013.

[3] A. Shrivastava and G. Banerjee, “Functional Testing of On-chip Analog/RF Circuits using Machine Learning based Regression Models”, IEEE International Test Conference India, Bangalore, India, July 2022.

Faculty: Prof. Gaurab Banerjee